Product Summary

The K4S561632J-UI75 is a synchronous high data rate Dynamic RAM. The K4S561632J-UI75 is fabricated with SAMSUNG’s high performance CMOS technology. Synchronous design allows precise cycle control with the use of system clock I/O transactions are possible on every clock cycle. Range of operating frequencies, programmable burst length and programmable latencies allow the same device to be useful for a variety of high bandwidth, high performance memory system applications.

Parametrics

K4S561632J-UI75 absolute maximum ratings: (1)Voltage on any pin relative to VSS:-1.0 to 4.6 V; (2)Voltage on VDD supply relative to VSS:-1.0 to 4.6 V; (3)Storage temperature:-55℃ to +150℃; (4)Power dissipation:1W; (5)Short circuit current:50 mA.

Features

K4S561632J-UI75 features: (1)JEDEC standard 3.3V power supply ; (2)LVTTL compatible with multiplexed address; (3)Four banks operation ; (4)MRS cycle with address key programs: CAS latency (2 & 3), Burst length (1, 2, 4, 8 & Full page), Burst type (Sequential & Interleave); (5)All inputs are sampled at the positive going edge of the system clock; (6)Burst read single-bit write operation; (7)DQM (x4,x8) & L(U)DQM (x16) for masking; (8)Auto & self refresh; (9)64ms refresh period (8K Cycle); (10)Lead-Free & Halogen-Free Package; (11)RoHS compliant.

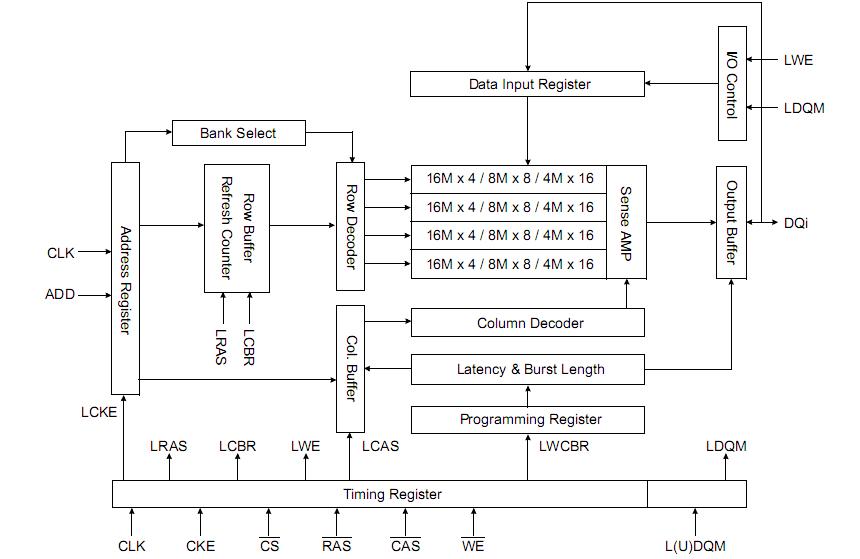

Diagrams

|

K4S510432B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4S510832B |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4S510832M |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4S511533F - Y(P)C |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4S511533F - Y(P)F |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

K4S511533F - Y(P)L |

Other |

|

Data Sheet |

Negotiable |

|

||||

(Hong Kong)

(Hong Kong)